![]() Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä SMSC, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ IBM

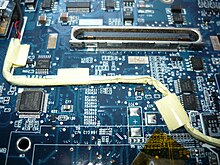

Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä SMSC, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ IBM

Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä Winbond W83977EF, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ

Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä Winbond W83977EF, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ

Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä SMSC, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ –Ω–æ—É—Ç–±—É–∫–∞ Samsung

Super I/O –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä SMSC, –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∏–π –Ω–∞ –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫—ñ–π –ø–ª–∞—Ç—ñ –Ω–æ—É—Ç–±—É–∫–∞ Samsung

Super I/O (англ. Super Input/output; дослівно: супер <контролер> введення/виведення) — назва класу співпроцесорів, які почали використовуватися після 1980-х років на материнських платах IBM PC-сумісних комп'ютерів шляхом поєднання функцій багатьох контролерів, спершу однією платою встановлюваною в слот розширення, а потім однією мікросхемою, тим самим досягаючи зменшення числа мікросхем контролерів. Таким чином це привело до зниження складності та вартості комп'ютера в цілому. Super I/O об'єднує інтерфейси різних низькочастотних пристроїв.

–°–ø–æ—á–∞—Ç–∫—É Super I/O –∑–≤'—è–∑—É–≤–∞–ª–∏—Å—è —á–µ—Ä–µ–∑ —à–∏–Ω—É ISA. –û–¥–Ω–æ—á–∞—Å–Ω–æ –∑ —Ä–æ–∑–≤–∏—Ç–∫–æ–º IBM PC-—Å—É–º—ñ—Å–Ω–∏—Ö –∫–æ–º–ø'—é—Ç–µ—Ä—ñ–≤ –≤—ñ–¥–±—É–≤–∞–ª–æ—Å—è –∑–º—ñ—â–µ–Ω–Ω—è Super I/O, —Å–ø–µ—Ä—à—É –Ω–∞ —à–∏–Ω–∏ VLB, –ø–æ—Ç—ñ–º —Å—Ç–∞–ª–∞ –≤–∏–∫–æ—Ä–∏—Å—Ç–æ–≤—É–≤–∞—Ç–∏—Å—è —à–∏–Ω–∞ PCI. –°—É—á–∞—Å–Ω—ñ Super I/O –≤–∏–∫–æ—Ä–∏—Å—Ç–æ–≤—É—é—Ç—å —à–∏–Ω—É LPC (—ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å —è–∫–æ—ó –Ω–∞–¥–∞—î –ø—ñ–≤–¥–µ–Ω–Ω–∏–π –º—ñ—Å—Ç –º–∞—Ç–µ—Ä–∏–Ω—Å—å–∫–æ—ó –ø–ª–∞—Ç–∏) —Ç–∞ —á–∞—Å—Ç–æ —Ä–µ–∞–ª—ñ–∑–æ–≤–∞–Ω—ñ —É —Å–∫–ª–∞–¥—ñ —á–∏–ø—Å–µ—Ç—É.

–§—É–Ω–∫—Ü—ñ—ó

Super I/O, —è–∫ –ø—Ä–∞–≤–∏–ª–æ, –º—ñ—Å—Ç–∏—Ç—å –Ω–∞—Å—Ç—É–ø–Ω—ñ –ø—ñ–¥—Å–∏—Å—Ç–µ–º–∏:

Super I/O —Ç–∞–∫–æ–∂ –º–æ–∂–µ –º—ñ—Å—Ç–∏—Ç–∏ —ñ–Ω—à—ñ —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å–∏, —Ç–∞–∫—ñ —è–∫ —ñ–≥—Ä–æ–≤–∏–π (MIDI –∞–±–æ –¥–∂–æ–π—Å—Ç–∏–∫) –∞–±–æ —ñ–Ω—Ñ—Ä–∞—á–µ—Ä–≤–æ–Ω–∏–π –ø–æ—Ä—Ç–∏.

–ü—Ä–∏–∫–ª–∞–¥ —Ä–µ–∞–ª—ñ–∑–∞—Ü—ñ—ó

–ü—Ä–∏–∫–ª–∞–¥–æ–º Super I/O –º–æ–∂–µ —Å–ª—É–∂–∏—Ç–∏ –º—ñ–∫—Ä–æ—Å—Ö–µ–º–∞ Intel 631xESB/632xESB, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î —Ç–∞–∫—ñ —Ñ—É–Ω–∫—Ü—ñ—ó[1]:

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Ä–µ–∞–ª—ñ–∑–∞—Ü—ñ—é —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å—É ESI (–∞–Ω–≥–ª. Enterprise South Bridge Interface, ESI) —ñ –ø–æ—Ä—Ç—É PCI Express, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î 8-–∫—Ä–∞—Ç–Ω–∏–π –ø–æ—Ç—ñ–∫ –ø–µ—Ä–µ–¥–∞—á—ñ –¥–æ Memory Controller Hub (MCH).

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Å—É–º—ñ—Å–Ω—ñ—Å—Ç—å –∑ –≤–µ—Ä—Å—ñ—î—é 1.0a —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—ó —à–∏–Ω–∏ PCI Express.

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Å—É–º—ñ—Å–Ω—ñ—Å—Ç—å –∑ –¥–æ–¥–∞—Ç–∫–æ–º –¥–æ –ø—Ä–æ—Ç–æ–∫–æ–ª—É —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—ó –≤–µ—Ä—Å—ñ—ó 2.0a —à–∏–Ω–∏ PCI —ñ –¥–æ–¥–∞—Ç–∫–æ–º –ø–æ –µ–ª–µ–∫—Ç—Ä–∏—á–Ω–æ—ó —Ç–∞ –º–µ—Ö–∞–Ω—ñ—á–Ω–æ—ó —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—ó —à–∏–Ω–∏ PCI.

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Å—É–º—ñ—Å–Ω—ñ—Å—Ç—å –∑ –≤–µ—Ä—Å—ñ—î—é 2.3 —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—ó —à–∏–Ω–∏ PCI –≤ —á–∞—Å—Ç–∏–Ω—ñ –ø—ñ–¥—Ç—Ä–∏–º–∫–∏ —Ä–æ–±–æ—Ç–∏ –Ω–∞ —á–∞—Å—Ç–æ—Ç—ñ 33 –ú–ì—Ü (–ø—ñ–¥—Ç—Ä–∏–º–∫–∞ –¥–æ —Å–µ–º–∏ –ø–∞—Ä Req/Gnt).

- –ó–∞–±–µ–∑–ø–µ—á—É—î –ª–æ–≥—ñ—á–Ω—É –ø—ñ–¥—Ç—Ä–∏–º–∫—É —Ä–µ–∂–∏–º—ñ–≤ —Å–ø–æ–∂–∏–≤–∞–Ω–Ω—è –∂–∏–≤–ª–µ–Ω–Ω—è ACPI.

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Ä–µ–∞–ª—ñ–∑–∞—Ü—ñ—é –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä–∞ Enhanced DMA, –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä–∞ –ø–µ—Ä–µ—Ä–∏–≤–∞–Ω—å —Ç–∞ —Ñ—É–Ω–∫—Ü—ñ—ó –≥–æ–¥–∏–Ω–Ω–∏–∫–∞ —Ä–µ–∞–ª—å–Ω–æ–≥–æ —á–∞—Å—É.

- –ú—ñ—Å—Ç–∏—Ç—å —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä SATA –∑ –Ω–µ–∑–∞–ª–µ–∂–Ω–∏–º–∏ DMA-–æ–ø–µ—Ä–∞—Ü—ñ—è–º–∏ –Ω–∞ —à–µ—Å—Ç–∏ –ø–æ—Ä—Ç–∞—Ö —Ç–∞ –ø—ñ–¥—Ç—Ä–∏–º–∫—É AHCI.

- –ú—ñ—Å—Ç–∏—Ç—å —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä IDE, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î —Ä–æ–±–æ—Ç—É —Ä–µ–∂–∏–º—ñ–≤ Ultra ATA100/66/33.

- –ú—ñ—Å—Ç–∏—Ç—å —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å—É USB –∑ –ø—ñ–¥—Ç—Ä–∏–º–∫–æ—é –≤–æ—Å—å–º–∏ –ø–æ—Ä—Ç—ñ–≤; –º—ñ—Å—Ç–∏—Ç—å —á–æ—Ç–∏—Ä–∏ —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏—Ö –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä–∞ UHCI; –∑–¥–æ–±—É–¥–µ –æ–¥–∏–Ω —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –≤–∏—Å–æ–∫–æ—à–≤–∏–¥–∫—ñ—Å–Ω–∏–π EHCI-–∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î —Ä–æ–±–æ—Ç—É –≤ —Ä–µ–∂–∏–º—ñ USB 2.0.

- –ú—ñ—Å—Ç–∏—Ç—å –∑–¥–≤–æ—î–Ω–∏–π –≥—ñ–≥–∞–±—ñ—Ç–æ–≤–∏–π MAC, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î —Ä–æ–±–æ—Ç—É –∑–≥—ñ–¥–Ω–æ –∑—ñ —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—è–º–∏ IEEE 802.3 –∑ –ø—ñ–¥—Ç—Ä–∏–º–∫–æ—é —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å—É SerDes[en][2]/Kumeran –¥–ª—è –¥–≤–æ—Ö PHY-–∫–æ–º–ø–æ–Ω–µ–Ω—Ç—ñ–≤.

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Ä–æ–±–æ—Ç—É PICMG-—Å—É–º—ñ—Å–Ω–æ–≥–æ –≥—ñ–≥–∞–±—ñ—Ç–æ–≤–æ–≥–æ Ethernet.

- –ú—ñ—Å—Ç–∏—Ç—å —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –∫–æ–Ω—Ç—Ä–æ–ª–µ—Ä –ø–ª–∞—Ç–∏ –∑ –±–∞–∑–æ–≤–∏–º –≤–±—É–¥–æ–≤–∞–Ω–∏–º –ü–ó, —â–æ –∑–∞–±–µ–∑–ø–µ—á—É—î —Ä–æ–∑—à–∏—Ä—é–≤–∞–Ω—ñ—Å—Ç—å —á–µ—Ä–µ–∑ –∑–æ–≤–Ω—ñ—à–Ω—é —Ñ–ª–µ—à-–ø–∞–º'—è—Ç—å —Ç–∞ –æ–ø–µ—Ä–∞—Ç–∏–≤–Ω—É –ø–∞–º'—è—Ç—å.

- –ó–∞–±–µ–∑–ø–µ—á—É—î —Å—É–º—ñ—Å–Ω—ñ—Å—Ç—å –∑ –≤–µ—Ä—Å—ñ—î—é 2.0 SMBus –∑ –¥–æ–¥–∞—Ç–∫–æ–≤–æ—é –ø—ñ–¥—Ç—Ä–∏–º–∫–æ—é I2C-–ø—Ä–∏—Å—Ç—Ä–æ—ó–≤.

- –ú—ñ—Å—Ç–∏—Ç—å —ñ–Ω—Ç–µ–≥—Ä–æ–≤–∞–Ω–∏–π –∞—É–¥—ñ–æ—ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å (AC '97 —Ç–∞ Intel High Definition Audio), –∞ —Ç–∞–∫–æ–∂ —Å–ø–µ—Ü–∏—Ñ—ñ–∫–∞—Ü—ñ—é –º–æ–¥–µ–º—É AC'97.

- –ú–∞—î —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å Low Pin Count.

- –ó–∞–±–µ–∑–ø–µ—á—É—î –ø—ñ–¥—Ç—Ä–∏–º–∫—É —ñ–Ω—Ç–µ—Ä—Ñ–µ–π—Å—É Firmware Hub (FWH).

- –ó–∞–±–µ–∑–ø–µ—á—É—î –¥–æ–¥–∞—Ç–∫–æ–≤—ñ —Ñ—É–Ω–∫—Ü—ñ—ó, –Ω–∞–ø—Ä–∏–∫–ª–∞–¥: –∫–µ—Ä—É—î –ø—Ä–æ—Ü–µ—Å–∞–º–∏ –ø—ñ–¥ —á–∞—Å –ø–µ—Ä–µ–∑–∞–≤–∞–Ω—Ç–∞–∂–µ–Ω–Ω—è —ñ —è–∫—â–æ –ø—ñ–¥ —á–∞—Å –ø–µ—Ä–≤—ñ—Å–Ω–æ–≥–æ —Å—Ç–∞—Ä—Ç—É —Ü–µ–Ω—Ç—Ä–∞–ª—å–Ω–∏–º –ø—Ä–æ—Ü–µ—Å–æ—Ä–æ–º –Ω–µ –ø–æ—á–∞–ª–∞—Å—å –≤–∏–∫–æ–Ω–∞–Ω–Ω—è —ñ–Ω—Å—Ç—Ä—É–∫—Ü—ñ–π, –ø–µ—Ä–µ–∑–∞–ø—É—Å–∫–∞—î –∫–æ–º–ø'—é—Ç–µ—Ä; –∞–±–æ –ø–µ—Ä–µ–≤–æ–¥–∏—Ç—å –∫–æ–º–ø'—é—Ç–µ—Ä –≤ —Ä–µ–∂–∏–º –∑—É–ø–∏–Ω—É —É –≤–∏–ø–∞–¥–∫—É —Å–ø—Ä–∞—Ü—é–≤–∞–Ω–Ω—è –∑–∞—Ö–∏—Å—Ç—É –ø—Ä–∏ –≤—ñ–¥–∫—Ä–∏—Ç—Ç—ñ –∫–æ—Ä–ø—É—Å—É —Å–∏—Å—Ç–µ–º–Ω–æ–≥–æ –±–ª–æ–∫—É.

–î–∏–≤. —Ç–∞–∫–æ–∂

–ü—Ä–∏–º—ñ—Ç–∫–∏

–ü–æ—Å–∏–ª–∞–Ω–Ω—è